# Intel<sup>®</sup> Desktop Board D946GZIS Technical Product Specification

September 2006

Order Number: D56025-002US

The Intel<sup>®</sup> Desktop Board D946GZIS may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the Intel Desktop Board D946GZIS Specification Update.

# **Revision History**

| Revision | Revision History Date                                                                                                                           |                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | First release of the Intel <sup>®</sup> Desktop Board D946GZIS Technical Product Specification.                                                 | July 2006      |

| -002     | Second release of the Intel <sup>®</sup> Desktop Board D946GZIS Technical Product Specification. Removed references to DDR2 800 memory support. | September 2006 |

This product specification applies to only the standard Intel<sup>®</sup> Desktop Board D946GZIS with BIOS identifier TS94610J.86A.

Changes to this specification will be published in the Intel Desktop Board D946GZIS Specification Update before being incorporated into a revision of this document.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel<sup>®</sup> desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel, the Intel logo, Pentium, and Celeron are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright © 2006, Intel Corporation. All rights reserved.

This Technical Product Specification (TPS) specifies the board layout, components, connectors, power and environmental requirements, and the BIOS for the Intel<sup>®</sup> Desktop Board D946GZIS. It describes the standard product and available manufacturing options.

# **Intended Audience**

The TPS is intended to provide detailed, technical information about the Desktop Board D946GZIS and its components to the vendors, system integrators, and other engineers and technicians who need this level of information. It is specifically *not* intended for general audiences.

## **What This Document Contains**

#### **Chapter** Description

- 1 A description of the hardware used on the board

- 2 A map of the resources of the bard

- 3 The features supported by the BIOS Setup program

- 4 A description of the BIOS error messages, beep codes, and POST codes

## **Typographical Conventions**

This section contains information about the conventions used in this specification. Not all of these symbols and abbreviations appear in all specifications of this type.

## Notes, Cautions, and Warnings

#### **≡**> NOTE

Notes call attention to important information.

## 🛠 INTEGRATOR'S NOTES

Integrator's notes are used to call attention to information that may be useful to system integrators.

##

Cautions are included to help you avoid damaging hardware or losing data.

| #         | Used after a signal name to identify an active-low signal (such as USBPO#)                                     |

|-----------|----------------------------------------------------------------------------------------------------------------|

| GB        | Gigabyte (1,073,741,824 bytes)                                                                                 |

| GB/sec    | Gigabytes per second                                                                                           |

| Gbit      | Gigabit (1,073,741,824 bits)                                                                                   |

| КВ        | Kilobyte (1024 bytes)                                                                                          |

| Kbit      | Kilobit (1024 bits)                                                                                            |

| kbits/sec | 1000 bits per second                                                                                           |

| MB        | Megabyte (1,048,576 bytes)                                                                                     |

| MB/sec    | Megabytes per second                                                                                           |

| Mbit      | Megabit (1,048,576 bits)                                                                                       |

| Mbit/sec  | Megabits per second                                                                                            |

| xxh       | An address or data value ending with a lowercase h indicates a hexadecimal value.                              |

| x.x V     | Volts. Voltages are DC unless otherwise specified.                                                             |

| *         | This symbol is used to indicate third-party brands and names that are the property of their respective owners. |

## **Other Common Notation**

## **1** Product Description

|   | 1.1  | Overvie              | ew                                       | 10 |

|---|------|----------------------|------------------------------------------|----|

|   |      | 1.1.1                | Feature Summary                          | 10 |

|   |      | 1.1.2                | Board Layout                             | 12 |

|   |      | 1.1.3                | Block Diagram                            | 14 |

|   | 1.2  | Online S             | Support                                  | 15 |

|   | 1.3  | Process              | or                                       | 15 |

|   | 1.4  | System               | Memory                                   | 16 |

|   |      | 1.4.1                | Memory Configurations                    | 18 |

|   | 1.5  | Intel <sup>®</sup> 9 | 946GZ Express Chipset                    | 21 |

|   |      | 1.5.1                | Intel 946GZ Graphics Subsystem           |    |

|   |      | 1.5.2                | USB                                      |    |

|   |      | 1.5.3                | Serial ATA Interfaces                    | 24 |

|   |      | 1.5.4                | Parallel IDE Interface                   |    |

|   |      | 1.5.5                | Real-Time Clock, CMOS SRAM, and Battery  | 26 |

|   | 1.6  | Legacy               | I/O Controller                           |    |

|   |      | 1.6.1                | Serial Port                              | 30 |

|   |      | 1.6.2                | Parallel Port                            |    |

|   |      | 1.6.3                | Diskette Drive Controller                |    |

|   |      | 1.6.4                | Keyboard and Mouse Interface             |    |

|   | 1.7  |                      | Subsystem                                |    |

|   |      | 1.7.1                | Audio Subsystem Software                 |    |

|   |      | 1.7.2                | Audio Connectors and Headers             |    |

|   | 1.8  |                      | bsystem                                  |    |

|   |      | 1.8.1                | Intel <sup>®</sup> 82562G PLC Device     |    |

|   |      | 1.8.2                | LAN Subsystem Software                   |    |

|   |      | 1.8.3                | RJ-45 LAN Connector with Integrated LEDs |    |

|   | 1.9  |                      | re Management Subsystem                  |    |

|   |      | 1.9.1                | Hardware Monitoring and Fan Control      |    |

|   |      | 1.9.2                | Fan Monitoring                           | 34 |

|   |      | 1.9.3                | Chassis Intrusion and Detection          |    |

|   |      | 1.9.4                | Thermal Monitoring                       |    |

|   | 1.10 |                      | Management                               |    |

|   |      |                      | ACPI                                     |    |

|   |      | 1.10.2               | Hardware Support                         | 38 |

| 2 | Tec  | hnical               | Reference                                |    |

|   | 2.1  | Memory               | у Мар                                    | 43 |

|   |      | 2.1.1                | Addressable Memory                       |    |

|   | 2.2  |                      | nannels                                  |    |

|   |      |                      | О Мар                                    |    |

|   | 2.4  | PCI Cor              | nfiguration Space Map                    | 47 |

|   | 2.5  |                      | pts                                      |    |

|   |      |                      |                                          |    |

|   |                                                                                                                    |                                                                                                                                                                              | errupt Routing Map                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

|---|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|   | 2.7                                                                                                                |                                                                                                                                                                              | tors and Headers                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|   |                                                                                                                    | 2.7.1                                                                                                                                                                        | Back Panel Connectors                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|   |                                                                                                                    | 2.7.2                                                                                                                                                                        | Component-side Connectors and Headers                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|   | 2.8                                                                                                                |                                                                                                                                                                              | Block                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|   | 2.9                                                                                                                |                                                                                                                                                                              | ical Considerations                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                      |

|   |                                                                                                                    | 2.9.1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

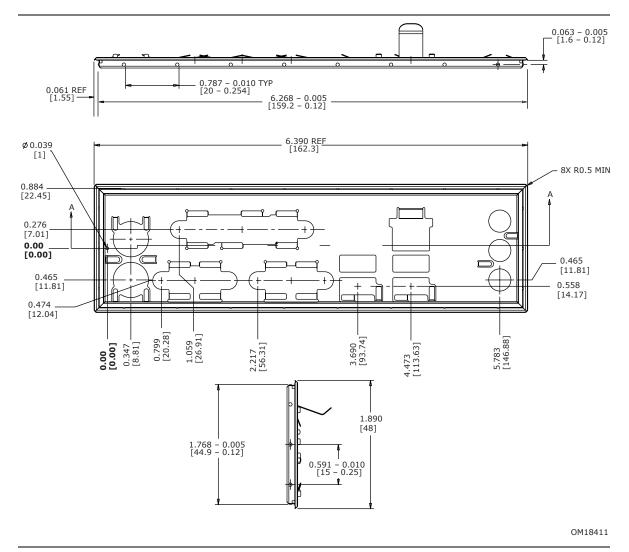

|   |                                                                                                                    | 2.9.2                                                                                                                                                                        | I/O Shield                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|   | 2.10                                                                                                               |                                                                                                                                                                              | al Considerations                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

|   |                                                                                                                    |                                                                                                                                                                              | DC Loading                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|   |                                                                                                                    |                                                                                                                                                                              | Fan Header Current Capability                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|   |                                                                                                                    | 2.10.3                                                                                                                                                                       | Add-in Board Considerations                                                                                                                                                                                                                                                                                                                                                                                             | 64                                                                                     |

|   |                                                                                                                    | 2.10.4                                                                                                                                                                       | Power Supply Considerations                                                                                                                                                                                                                                                                                                                                                                                             | 64                                                                                     |

|   | 2.11                                                                                                               | Therma                                                                                                                                                                       | al Considerations                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                     |

|   | 2.12                                                                                                               | Reliabil                                                                                                                                                                     | ity                                                                                                                                                                                                                                                                                                                                                                                                                     | 67                                                                                     |

|   | 2.13                                                                                                               | Environ                                                                                                                                                                      | imental                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                                                     |

|   | 2.14                                                                                                               | Regulat                                                                                                                                                                      | cory Compliance                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                     |

|   |                                                                                                                    |                                                                                                                                                                              | Safety Regulations                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

|   |                                                                                                                    | 2.14.2                                                                                                                                                                       | European Union Declaration of Conformity Statement                                                                                                                                                                                                                                                                                                                                                                      | 68                                                                                     |

|   |                                                                                                                    |                                                                                                                                                                              | Product Ecology Statements                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|   |                                                                                                                    |                                                                                                                                                                              | EMC Regulations                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|   |                                                                                                                    | 2.14.5                                                                                                                                                                       | Product Certification Markings (Board Level)                                                                                                                                                                                                                                                                                                                                                                            | 74                                                                                     |

|   |                                                                                                                    |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 3 | Ove                                                                                                                | erview                                                                                                                                                                       | of BIOS Features                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| 3 |                                                                                                                    |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                     |

| 3 | 3.1                                                                                                                | Introdu                                                                                                                                                                      | ction                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| 3 | 3.1<br>3.2                                                                                                         | Introdu<br>BIOS F                                                                                                                                                            | ction<br>lash Memory Organization                                                                                                                                                                                                                                                                                                                                                                                       | 76                                                                                     |

| 3 | 3.1                                                                                                                | Introdu<br>BIOS Fl<br>Resourc                                                                                                                                                | ction<br>lash Memory Organization<br>ce Configuration                                                                                                                                                                                                                                                                                                                                                                   | 76<br>76                                                                               |

| 3 | 3.1<br>3.2                                                                                                         | Introdu<br>BIOS Fl<br>Resourc<br>3.3.1                                                                                                                                       | ction<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration                                                                                                                                                                                                                                                                                                                                          | 76<br>76<br>76                                                                         |

| 3 | 3.1<br>3.2<br>3.3                                                                                                  | Introdu<br>BIOS Fl<br>Resourc<br>3.3.1<br>3.3.2                                                                                                                              | ction<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support                                                                                                                                                                                                                                                                                                                       | 76<br>76<br>76<br>77                                                                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                                                                           | Introdu<br>BIOS Fl<br>Resourc<br>3.3.1<br>3.3.2<br>System                                                                                                                    | ction<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)                                                                                                                                                                                                                                                                                           | 76<br>76<br>76<br>77<br>77                                                             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                    | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy                                                                                                          | Iction<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support                                                                                                                                                                                                                                                                           | 76<br>76<br>76<br>77<br>77<br>78                                                       |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                                                                           | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U                                                                                                | Iction<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates                                                                                                                                                                                                                                                                 | 76<br>76<br>77<br>77<br>78<br>78                                                       |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                    | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1                                                                                       | Action<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support                                                                                                                                                                                                                                             | 76<br>76<br>77<br>77<br>78<br>78<br>78<br>79                                           |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2                                                                              | Inction<br>Iash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen                                                                                                                                                                                                                    | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79                                           |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op                                                                   | ash Memory Organization<br>lash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>USB Support<br>Language Support<br>Custom Splash Screen                                                                                                                                                                                               | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79<br>79                                     |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1                                                          | Action<br>Ash Memory Organization<br>PCI Autoconfiguration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen<br>ptions<br>CD-ROM Boot                                                                                                                                                                                        | 76<br>76<br>77<br>77<br>78<br>79<br>79<br>79<br>79<br>79                               |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2                                                 | Action<br>Ash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen<br>ptions<br>CD-ROM Boot<br>Network Boot                                                                                                                                                                             | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79<br>79<br>79<br>79<br>79                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3                                        | Inction<br>Iash Memory Organization                                                                                                                                                                                                                                                                                                                                                                                     | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79<br>79<br>79<br>79<br>80                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                                      | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.3                               | Ash Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                 | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79<br>79<br>79<br>79<br>80<br>80             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>Adjustin                   | Inction<br>Iash Memory Organization                                                                                                                                                                                                                                                                                                                                                                                     | 76<br>76<br>77<br>77<br>78<br>78<br>79<br>79<br>79<br>79<br>79<br>79<br>80<br>80<br>80 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                                      | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>Adjustin<br>3.8.1          | Inction<br>Iash Memory Organization<br>Ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen<br>ptions<br>CD-ROM Boot<br>Network Boot<br>Booting Without Attached Devices<br>Changing the Default Boot Device During POST<br>ng Boot Speed<br>Peripheral Selection and Configuration                            | 76<br>76<br>77<br>77<br>78<br>79<br>79<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>80 |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>Adjustin<br>3.8.1<br>3.8.2 | Inction<br>Iash Memory Organization<br>ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen<br>otions<br>CD-ROM Boot<br>Network Boot<br>Booting Without Attached Devices<br>Changing the Default Boot Device During POST<br>ng Boot Speed<br>Peripheral Selection and Configuration<br>BIOS Boot Optimizations | 76<br>76<br>77<br>77<br>78<br>79<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>80<br>81 |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Introdu<br>BIOS Fl<br>Resourd<br>3.3.1<br>3.3.2<br>System<br>Legacy<br>BIOS U<br>3.6.1<br>3.6.2<br>Boot Op<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>Adjustin<br>3.8.1<br>3.8.2 | Inction<br>Iash Memory Organization<br>Ce Configuration<br>PCI Autoconfiguration<br>PCI IDE Support<br>Management BIOS (SMBIOS)<br>USB Support<br>pdates<br>Language Support<br>Custom Splash Screen<br>ptions<br>CD-ROM Boot<br>Network Boot<br>Booting Without Attached Devices<br>Changing the Default Boot Device During POST<br>ng Boot Speed<br>Peripheral Selection and Configuration                            | 76<br>76<br>77<br>77<br>78<br>79<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>80<br>81 |

| 4.1 | Speaker         | 83 |

|-----|-----------------|----|

| 4.2 | BIOS Beep Codes | 83 |

| 4.3 | BIOS Error Messages | 83 |

|-----|---------------------|----|

| 4.4 | Port 80h POST Codes | 84 |

## Figures

| 1.  | Major Board Components                                        | 12 |

|-----|---------------------------------------------------------------|----|

| 2.  | Block Diagram                                                 | 14 |

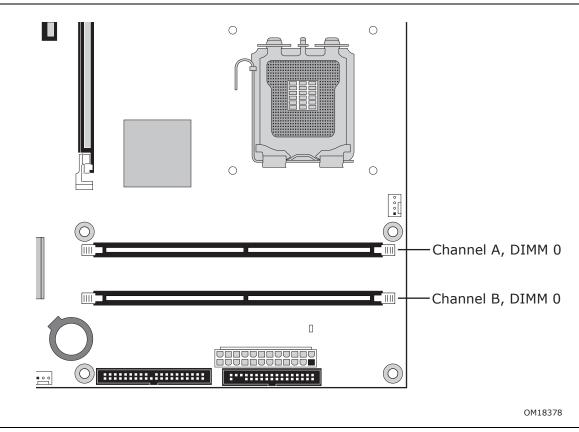

| 3.  | Memory Channel and DIMM Configuration                         | 18 |

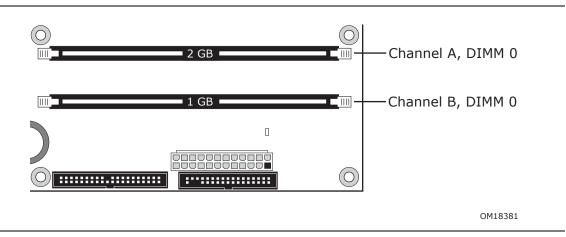

| 4.  | Dual Channel (Interleaved) Mode Configuration with Two DIMMs  | 19 |

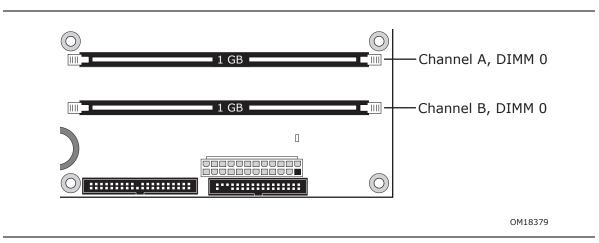

| 5.  | Single Channel (Asymmetric) Mode Configuration with One DIMM  | 20 |

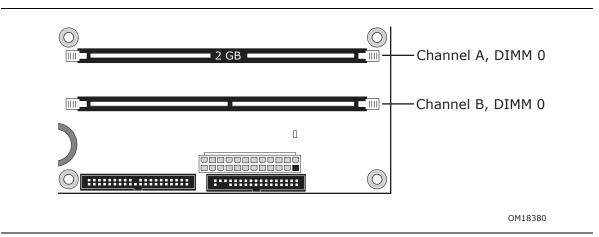

| 6.  | Single Channel (Asymmetric) Mode Configuration with Two DIMMs |    |

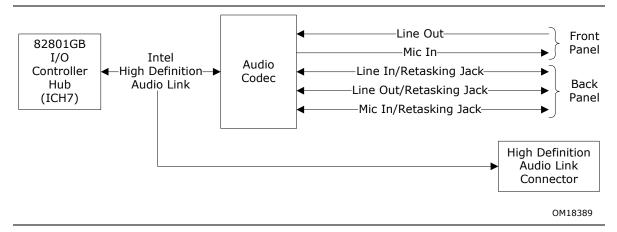

| 7.  | 6-Channel (5.1) Audio Subsystem Block Diagram                 | 31 |

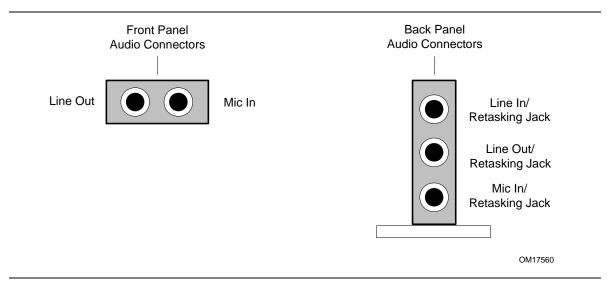

| 8.  | Front/Back Panel Audio Connector Options                      |    |

| 9.  | LAN Connector LED Locations                                   | 33 |

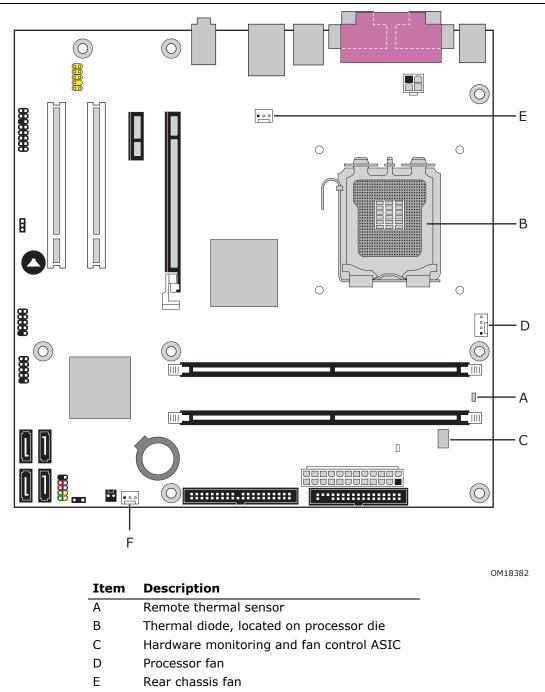

| 10. | Thermal Sensors and Fan Headers                               |    |

| 11. | Location of the Standby Power Indicator LED                   |    |

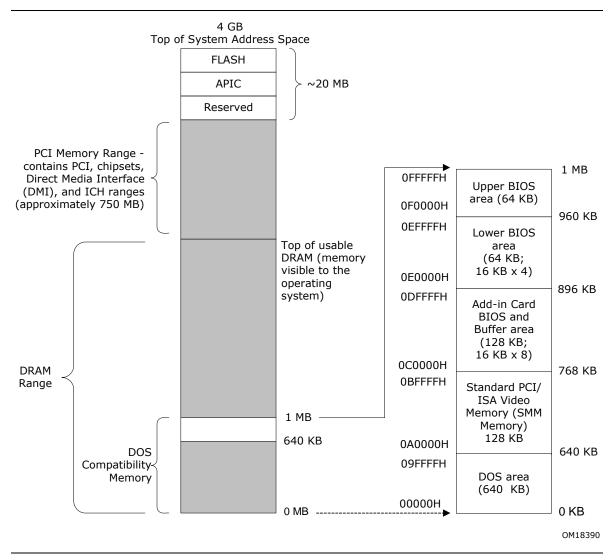

| 12. | Detailed System Memory Address Map                            |    |

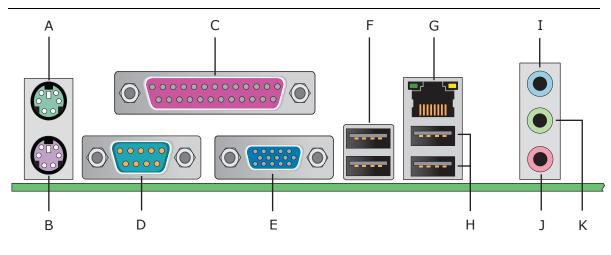

| 13. | Back Panel Connectors                                         |    |

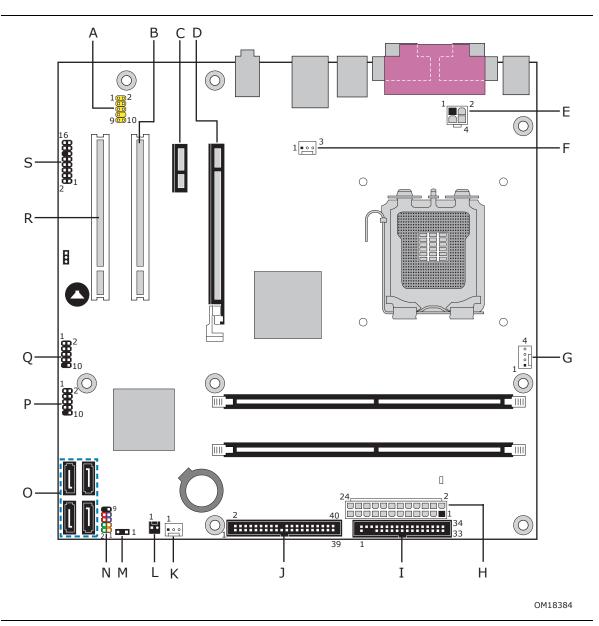

| 14. | Component-side Connectors and Headers                         |    |

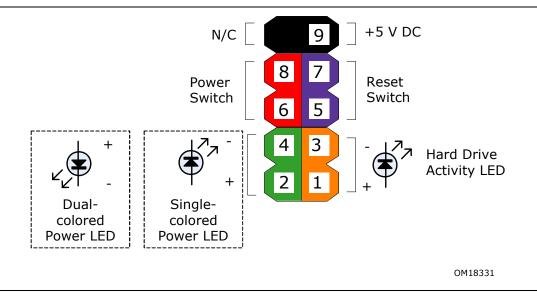

| 15. | Connection Diagram for Front Panel Header                     |    |

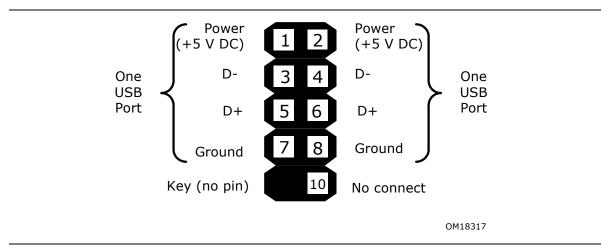

| 16. | Connection Diagram for Front Panel USB Headers                | 59 |

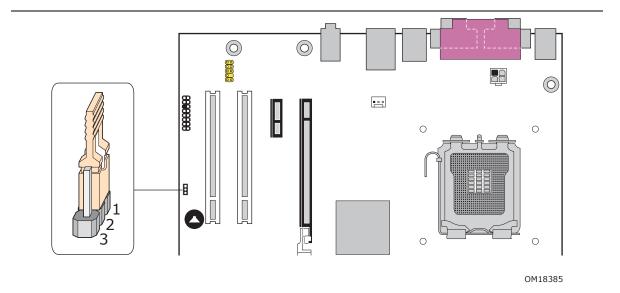

| 17. | Location of the Jumper Block                                  | 60 |

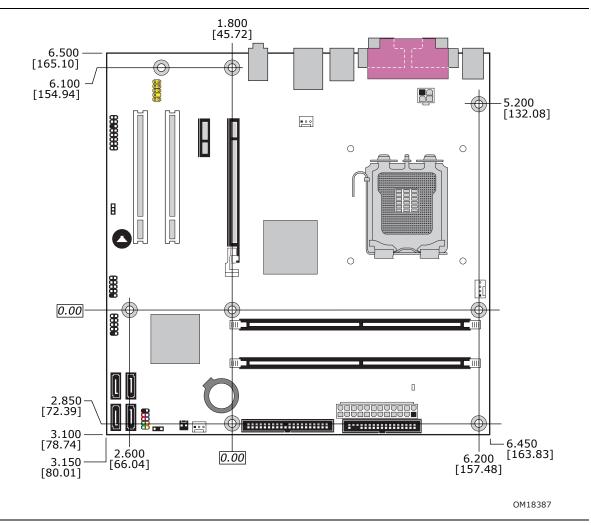

| 18. | Board Dimensions                                              |    |

| 19. | I/O Shield Dimensions                                         |    |

| 20. | Localized High Temperature Zones                              | 66 |

## Tables

| Feature Summary                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board Components Shown in Figure 1                       | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Memory Operating Frequencies                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LAN Connector LED States                                 | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Effects of Pressing the Power Switch                     | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power States and Targeted System Power                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Wake-up Devices and Events                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| System Memory Map                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Мар                                                  | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PCI Configuration Space Map                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupts                                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PCI Interrupt Routing Map                                | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Component-side Connectors and Headers Shown in Figure 14 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chassis Intrusion Header                                 | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          | Feature Summary<br>Board Components Shown in Figure 1<br>Supported Memory Configurations<br>Memory Operating Frequencies<br>LAN Connector LED States<br>Effects of Pressing the Power Switch<br>Power States and Targeted System Power.<br>Wake-up Devices and Events<br>System Memory Map<br>DMA Channels.<br>I/O Map<br>PCI Configuration Space Map<br>Interrupts<br>PCI Interrupt Routing Map<br>Component-side Connectors and Headers Shown in Figure 14.<br>Front Panel Audio Header<br>Front and Rear Chassis Fan Headers<br>Processor Fan Header<br>Chassis Intrusion Header. |

| 20. | Serial ATA Connectors                               | 54 |

|-----|-----------------------------------------------------|----|

| 21. | High Definition Audio Link Header                   | 54 |

| 22. | Processor Core Power Connector                      | 56 |

| 23. | Main Power Connector                                | 56 |

| 24. | Front Panel Header                                  | 57 |

| 25. | States for a One-Color Power LED                    |    |

| 26. | States for a Two-Color Power LED                    | 58 |

| 27. | BIOS Setup Configuration Jumper Settings            | 60 |

| 28. | DC Loading Characteristics                          | 63 |

| 29. | Fan Header Current Capability                       |    |

| 30. | Thermal Considerations for Components               |    |

| 31. | Desktop Board D946GZIS Environmental Specifications | 67 |

| 32. | Safety Regulations                                  |    |

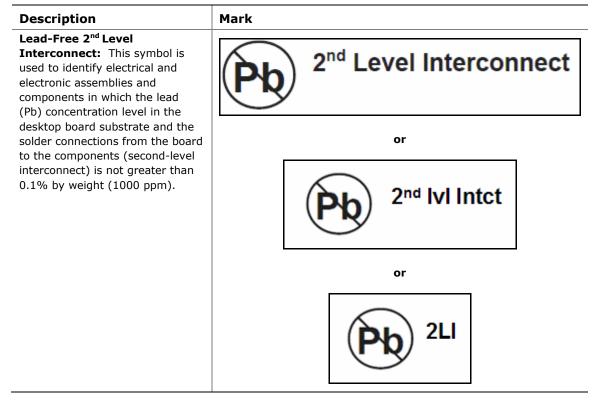

| 33. | Lead-Free Board Markings                            |    |

| 34. | EMC Regulations                                     |    |

| 35. | Product Certification Markings                      |    |

| 36. | BIOS Setup Program Menu Bar                         |    |

| 37. | BIOS Setup Program Function Keys                    |    |

| 38. | Boot Device Menu Options                            |    |

| 39. | Supervisor and User Password Functions              |    |

| 40. | Beep Codes                                          |    |

| 41. | BIOS Error Messages                                 |    |

| 42. | Port 80h POST Code Ranges                           |    |

| 43. | Port 80h POST Codes                                 |    |

| 44. | Typical Port 80h POST Sequence                      | 88 |

# What This Chapter Contains

| Overview                                 | 10                                                                                                                                                                                     |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Online Support                           | 15                                                                                                                                                                                     |

| Processor                                | 15                                                                                                                                                                                     |

| System Memory                            |                                                                                                                                                                                        |

| Intel <sup>®</sup> 946GZ Express Chipset | 21                                                                                                                                                                                     |

| Legacy I/O Controller                    |                                                                                                                                                                                        |

| Audio Subsystem                          | 31                                                                                                                                                                                     |

| LAN Subsystem                            | 33                                                                                                                                                                                     |

| Hardware Management Subsystem            | 34                                                                                                                                                                                     |

| Power Management                         | 36                                                                                                                                                                                     |

|                                          | Online Support<br>Processor<br>System Memory<br>Intel <sup>®</sup> 946GZ Express Chipset<br>Legacy I/O Controller<br>Audio Subsystem<br>LAN Subsystem<br>Hardware Management Subsystem |

## 1.1 Overview

## 1.1.1 Feature Summary

Table 1 summarizes the major features of the Desktop Board D946GZIS.

| Form Factor           | microATX (9.60 inches by 9.60 inches [243.84 millimeters by 243.84 millimeters]                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Processor             | Support for the following:                                                                                                      |

|                       | <ul> <li>Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor in an LGA775 socket with a 1066 or 800 MHz<br/>system bus</li> </ul> |

|                       | <ul> <li>Intel<sup>®</sup> Pentium<sup>®</sup> D processor in an LGA775 socket with an 800 or 533 MHz system bus</li> </ul>     |

|                       | - Intel $^{\textcircled{R}}$ Pentium $^{\textcircled{R}}$ 4 processor in an LGA775 socket with an 800 or 533 MHz system bus     |

|                       | - Intel^® Celeron^® D processor in an LGA775 socket with a 533 MHz system bus                                                   |

| Memory                | Two 240-pin DDR2 SDRAM Dual Inline Memory Module (DIMM) sockets                                                                 |

|                       | Support for DDR2 667 or DDR2 533 MHz DIMMs                                                                                      |

|                       | Support for up to 4 GB of system memory                                                                                         |

| Chipset               | Intel <sup>®</sup> 946GZ Express Chipset, consisting of:                                                                        |

|                       | • Intel <sup>®</sup> 82946GZ Graphics and Memory Controller Hub (GMCH)                                                          |

|                       | Intel <sup>®</sup> 82801GB I/O Controller Hub (ICH7)                                                                            |

| Video                 | Intel <sup>®</sup> GMA 3000 onboard graphics subsystem                                                                          |

| Audio                 | 6-channel (5.1) audio subsystem using the ADI1988A (or SigmaTel* STAC9227) audio codec                                          |

| Legacy I/O<br>Control | Legacy I/O controller for diskette drive, serial, parallel, and PS/2* ports                                                     |

| USB                   | Support for USB 2.0 devices                                                                                                     |

| Peripheral            | Eight USB ports                                                                                                                 |

| Interfaces            | Four Serial ATA IDE interfaces                                                                                                  |

|                       | One Parallel ATA IDE interface with UDMA 33, ATA-66/100 support                                                                 |

|                       | One diskette drive interface                                                                                                    |

|                       | One serial port                                                                                                                 |

|                       | One parallel port                                                                                                               |

| LAN Support           | 10/100 Mbits/sec LAN subsystem using the Intel <sup>®</sup> 82562G Platform LAN Connect (PLC) device                            |

| BIOS                  | Intel <sup>®</sup> BIOS (resident in the SPI Flash device)                                                                      |

|                       | <ul> <li>Support for Advanced Configuration and Power Interface (ACPI), Plug and Play<br/>and SMBIOS</li> </ul>                 |

| Instantly             | Support for PCI Local Bus Specification Revision 2.3                                                                            |

| Available PC          | Support for PCI Express* Revision 1.0a                                                                                          |

| Technology            | Suspend to RAM support                                                                                                          |

|                       | Wake on PCI, RS-232, front panel, PS/2 devices, and USB ports                                                                   |

Table 1. Feature Summary

continued

| Expansion        | One PCI Express x16 bus add-in card connector              |

|------------------|------------------------------------------------------------|

| Capabilities     | One PCI Express x1 bus add-in card connector               |

|                  | Two PCI Conventional* bus connectors                       |

| Hardware Monitor | Voltage sense to detect out of range power supply voltages |

| Subsystem        | Thermal sense to detect out of range thermal values        |

|                  | Three fan headers                                          |

|                  | Three fan sense inputs used to monitor fan activity        |

#### Table 1. Feature Summary (continued)

| For information about                                   | Refer to             |

|---------------------------------------------------------|----------------------|

| Available configurations for the Desktop Board D946GZIS | Section 1.2, page 15 |

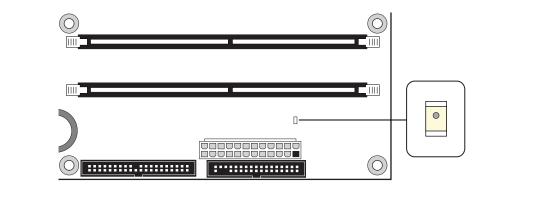

#### 1.1.2 Board Layout

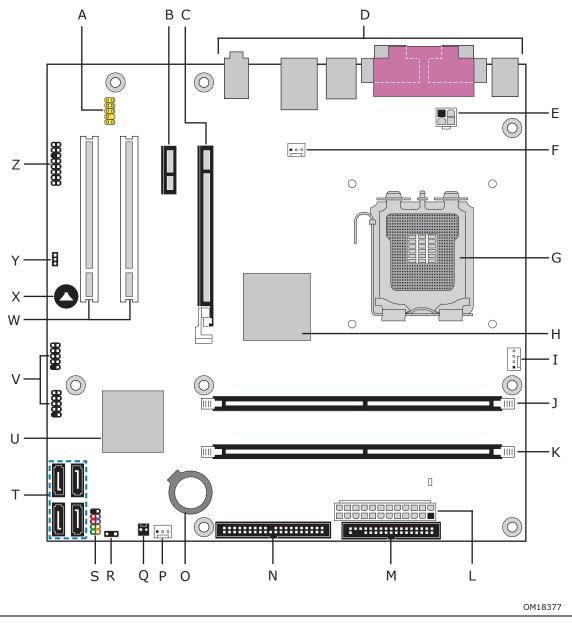

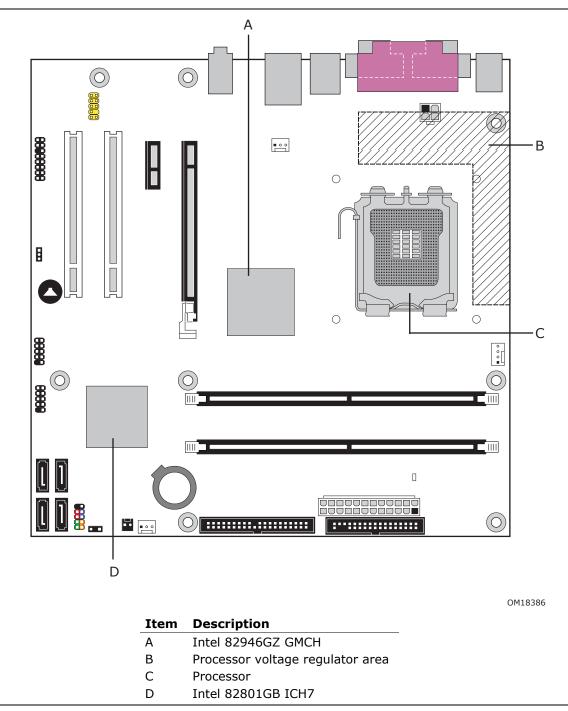

Figure 1 shows the location of the major components.

Figure 1. Major Board Components

Table 2 lists the components identified in Figure 1.

| AFront panel audio headerBPCI Express x1 connectorCPCI Express x16 connectorDBack panel connectorsEProcessor core power connectoFRear chassis fan headerGLGA775 processor socketHIntel 82946GZ GMCHIProcessor fan header |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CPCI Express x16 connectorDBack panel connectorsEProcessor core power connectoFRear chassis fan headerGLGA775 processor socketHIntel 82946GZ GMCH                                                                        |                   |

| DBack panel connectorsEProcessor core power connectoFRear chassis fan headerGLGA775 processor socketHIntel 82946GZ GMCH                                                                                                  |                   |

| EProcessor core power connectoFRear chassis fan headerGLGA775 processor socketHIntel 82946GZ GMCH                                                                                                                        |                   |

| FRear chassis fan headerGLGA775 processor socketHIntel 82946GZ GMCH                                                                                                                                                      |                   |

| GLGA775 processor socketHIntel 82946GZ GMCH                                                                                                                                                                              | r                 |

| H Intel 82946GZ GMCH                                                                                                                                                                                                     |                   |

|                                                                                                                                                                                                                          |                   |

| I Processor fan header                                                                                                                                                                                                   |                   |

|                                                                                                                                                                                                                          |                   |

| J DIMM Channel A socket                                                                                                                                                                                                  |                   |

| K DIMM Channel B socket                                                                                                                                                                                                  |                   |

| L Main Power connector                                                                                                                                                                                                   |                   |

| M Diskette drive connector                                                                                                                                                                                               |                   |

| N Parallel ATE IDE connector                                                                                                                                                                                             |                   |

| O Battery                                                                                                                                                                                                                |                   |

| P Front chassis fan header                                                                                                                                                                                               |                   |

| Q Chassis intrusion header                                                                                                                                                                                               |                   |

| R Auxiliary front panel power LED                                                                                                                                                                                        | ) header          |

| S Front panel header                                                                                                                                                                                                     |                   |

| T Serial ATA connectors [4]                                                                                                                                                                                              |                   |

| U Intel 82801GB I/O Controller H                                                                                                                                                                                         | ub (ICH7)         |

| V Front panel USB headers [2]                                                                                                                                                                                            |                   |

| W PCI Conventional bus add-in ca                                                                                                                                                                                         | rd connectors [2] |